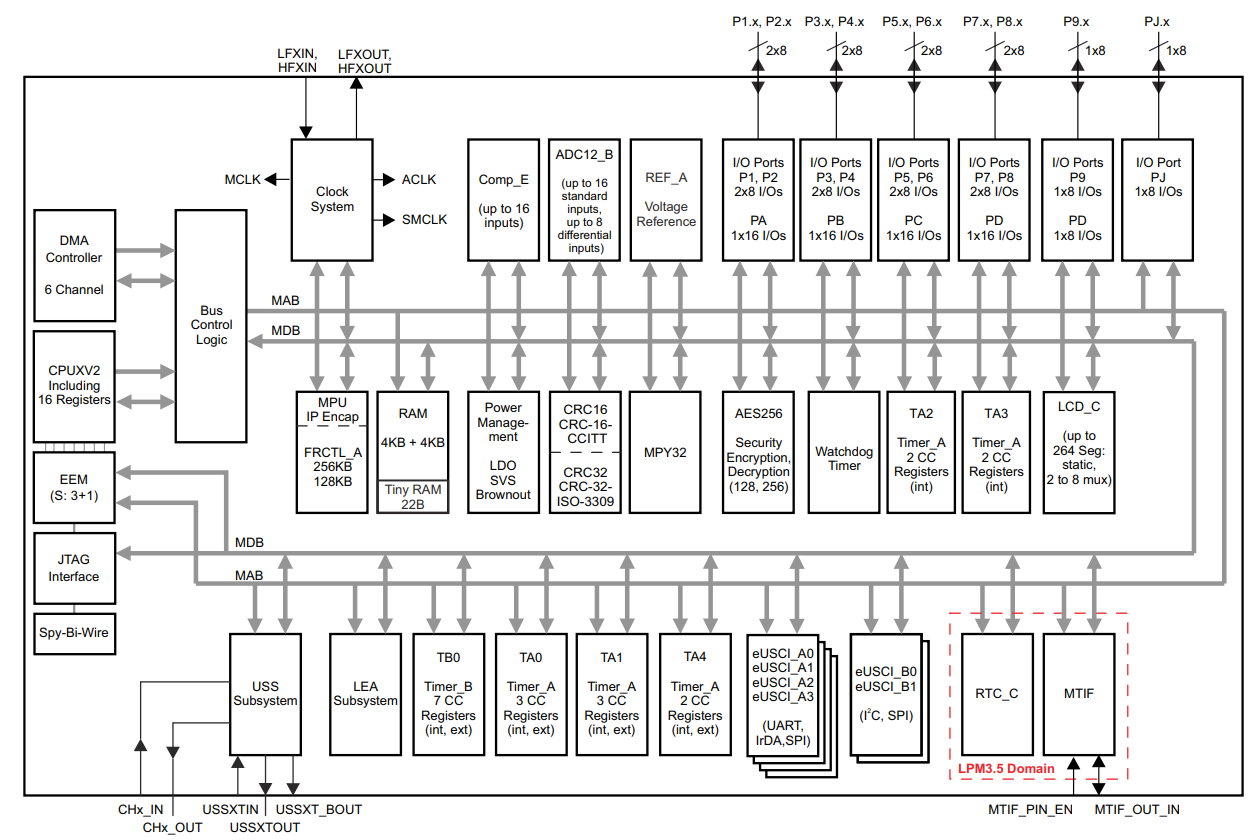

안녕하세요,UVM Testbench 작성 - WikiDocs 내용을 바탕으로 SystemVerilog에 대해 간단하게 정리해보았습니다. Verilog는 많이 접해볼 수 있는데 SystemVerilog는 자료 찾기가 상대적으로 좀 힘들었던 것 같습니다.이제 가볍게 훑어보면서 위키독스를 격파하도록 하겠습니다.반도체 칩 구조가 점차 복잡해지면서 검증의 중요성과 비중 또한 높아지고 있습니다.아래 그림은 SoC의 블록 다이어그램인데 이렇게 하나의 칩 내부는 여러 블록으로 구성되어 있습니다.이 블록을 모듈 또는 IP(Intellectual Property, 이하 IP)라고 합니다.과거에는 반도체 회사들이 IP를 직접 설계했지만, 이제는 IP 설계 업체로부터 검증된 IP를 구매해 칩을 설계합니다.IP를 직접 설계하는..