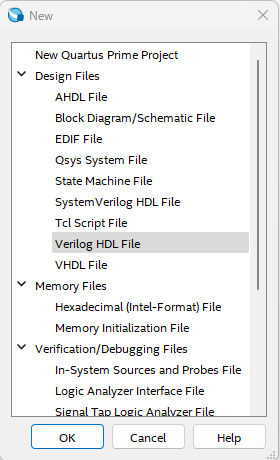

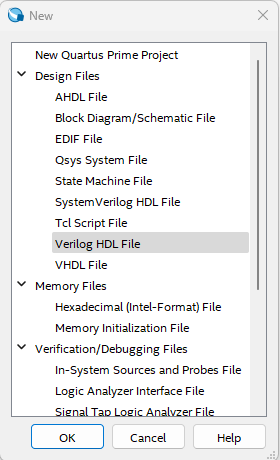

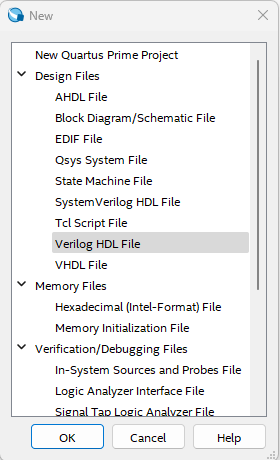

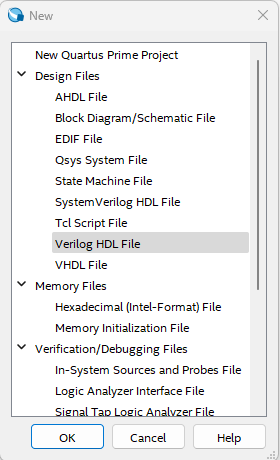

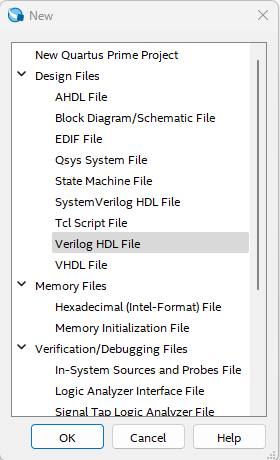

안녕하세요, 이번 글에서는 Verilog HDL로 asynchronous control 구현 및 그 결과를 테스트 벤치(Test Bench)로 확인하겠습니다. 환경 HDL : Verilog’ 2001 spec RTL Synthesis : Intel(Altera), Quartus prime 18.1 Functional Simulation : Intel(Altera), ModelSim 10.5b Quatus의 [File] → [New]에서 Verilog HDL File을 선택합니다. asynchronous control을 구현했습니다. module counter( inputclk, input aclr_n, output reg count_out ); always @ (posedge clk, negedge ac..