안녕하세요,

이번 글에서는 Verilog HDL로 2_input_mux를 구현하고, 그 결과를 테스트 벤치(Test Bench)로 확인하겠습니다.

환경

- HDL : Verilog’ 2001 spec

- RTL Synthesis : Intel(Altera), Quartus prime 18.1

- Functional Simulation : Intel(Altera), ModelSim 10.5b

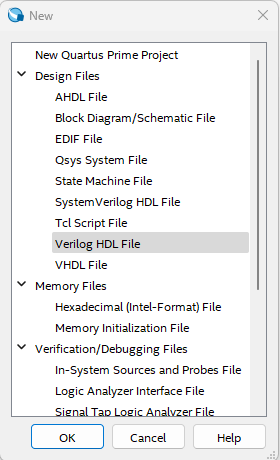

Quatus의 [File] → [New]에서 Verilog HDL File을 선택합니다.

2_input_mux를 구현했습니다.

module mux4(

input [4:0] mux_a ,

input [4:0] mux_b ,

input [1:0] mux_sel ,

output reg [4:0] mux_out

);

always @(*) begin

if(!mux_sel)

mux_out = mux_a ;

else

mux_out = mux_b ;

end

endmoduleVerilog HDL Check point

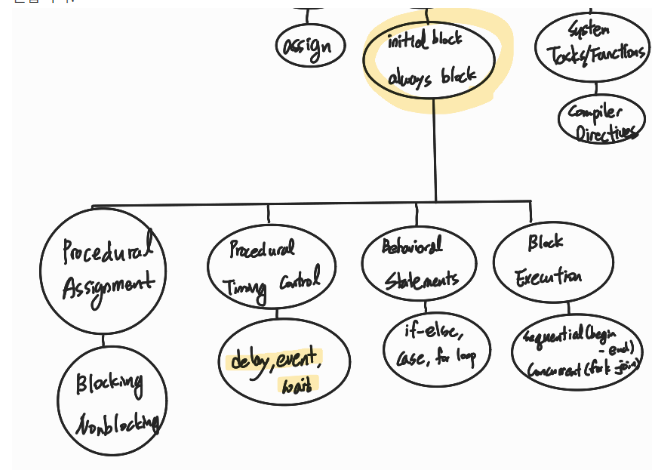

- if else 구문은 always, initial block에 속해 있으므로 꼭 always, initial 구문 안에서 사용해야 합니다.

- mux_sel이 1(0이 아닌 모든 값)이면 mux_a 값이 나오고, mux_sel이 0이면 mux_b 값이 나옵니다.

Test Bench를 작성했습니다.

`timescale 1 ns/1 ns

module mux4_tb();

reg [4:0] mux_a ;

reg [4:0] mux_b ;

reg [1:0] mux_sel ;

wire [4:0] mux_out ;

mux4 uMux4_0(

.mux_a (mux_a ),

.mux_b (mux_b ),

.mux_sel(mux_sel),

.mux_out(mux_out)

);

initial begin

mux_a = 5'd4 ;

mux_b = 5'd7 ;

mux_sel = 5'd1;

forever

#6 mux_sel = 5'd0 ;

end

endmoduleTest Bench Check point

- `timescale 1 ns/1 ns에서 앞의 1ns는 기본 단위 설정이며, 뒤의 1ns이며 이것을 구현하는 해상도는 1ns라는 뜻입니다.

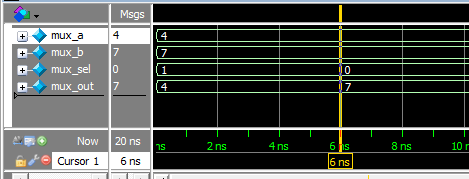

#6 mux_sel = 5'd0 ; 구문에서 #6는 6단위 시간 이후, mux_sel 값이 0이 된다는 뜻입니다.

그래서 처음 시작하고 mux_sel 값이 1이었다가 #6 mux_sel = 5'd0 구문에 의해 6ns 이후 mux_sel은 0이 됩니다.

- module과 endmodule로 module 시작 및 종료했습니다.

- 입력은 register인 reg로, 결과는 wire로 선언했습니다.

- mux4 Umux4_0은 instantation으로 Port name을 직접 Association 하는 방식을 사용했습니다.

다른 방식도 있으나 디버깅 효율을 높이기 위해 이 방법을 택했습니다. - mux_a의 초기 값은 4, mux_b의 초기 값은 7로 설정했습니다.

이제 ModelSim에서 시뮬레이션을 하기 위한 tcl파일을 만들겠습니다.

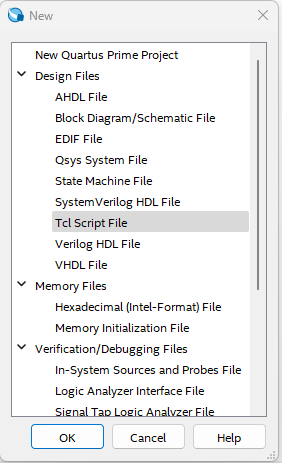

Quatus의 [File] → [New]에서 Tcl Script File을 선택합니다.

즉, 1번의 시뮬레이션을 위해서는 총 3개의 파일(Verilog HDL 기능 구현, TestBench, TCL)이 필요합니다.

vlib work

vlog mux4.v mux4_tb.v

vsim work.mux4_tb

add wave -radix dec /mux_a

add wave -radix dec /mux_b

add wave -radix dec /mux_sel

add wave -radix dec /mux_out

run 20 nsTCL file Check point

- vlib work, vlog, vsim work은 필수 항목입니다.

vlog 다음엔 verilog HDL 파일과 test bench 파일 이름이 나와야 합니다.

vsim work 다음 test bench 파일이 나와야 합니다. - add wave는 파형 추가입니다. dec는 decimal인 10진법입니다.

- '/' 다음 결과를 보고자 하는 변수를 입력하면 됩니다.

- run 이후 시뮬레이션 시간을 입력하면 됩니다.

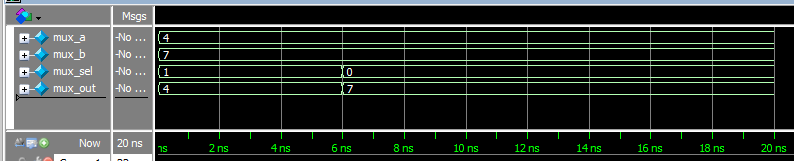

최종 결과