이번 글에서는 Delay, Event, Wait에 대해서 알아보겠습니다.

이들은 모두 initial과 always block에 사용되며 procedural block에 속합니다.

Verilog를 공부하면서 각 구문이 어디에 속하는지 확인하는 것이 참 중요하다는 것을 느껴 자주 확인합니다.

- Delay Control

Regular (Inter - Assignment) Delay Control과 Intra - Assignment Dealy Control 두 종류가 있습니다.

Regular (Inter - Assignment) Delay Control는 RHS와 LHS 동시에 적용됩니다. Blocking 구문에서 사용됩니다.

Intra - Assignment Dealy Control는 LHS만 적용됩니다. Non-Blocking 구문에서 사용됩니다.

이 둘의 차이점을 다음과 같은 상황에서 확인해 보겠습니다.

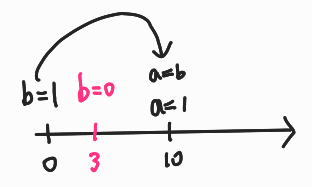

t = 0 에서 b = 1이고, t = 3 일 때 b = 0으로 변화하는 상황을 가정하겠습니다.

먼저 Regular (Inter - Assignment) Delay Control은

#10 a = b ; 이며 아래 사진에서 왼쪽과 같은 상황입니다. b 값이 중간에 변하면 바로 적용됩니다.

하지만

Intra - Assignment Dealy Control은 다릅니다.

a = #10 b ; 이며 아래 사진에서 오른쪽과 같은 상황입니다. b 값이 중간에 변해도 처음 b 값을 그대로 a에 적용합니다.

아래와 같다고 생각하시면 되겠습니다.

a = # 10 b ;

temp = b ;

#10 a = temp ;

- Event Control

Inter - Assignment로 클럭이 상승할 때마다 값을 할당하고 싶다면

@ (posedge clk) r1 = r2;

Intra-Assignment로 클럭이 하강할 때마다 값을 할당하고 싶다면

r3 = @ (negedge clk) r4;

- Wait

조건이 맞을 때까지 대기

ex) gate가 1일 때까지 대기하다 조건 충족 시 r1에 r2값 할당, gate가 0일 때까지 대기하다 조건 충족 시, r3에 r4값 할당

initial begin

wait (gate) r1 = r2;

wait (! gate) r3 = r4;

end

- if-else, case는 C 언어와 그 사용이 비슷합니다.

- loop statements는 forever loop, repeat loop, while loop, for loop가 있습니다.

forever loop - 계속 실행합니다.

ex) clock 발생 구문

initial begin

clk = 0 ;

forever #25 clk = ~clk ;

end

repeat loop - 지정한 횟수만큼 진행합니다.

ex)

if (rotate == 1)

repeat (8) begin

tmp = data [15];

data = {data [14:0], tmp} ;

end

while loop는 제시한 조건이 충족될 때까지 실행되고, for loop는 C언어의 for문과 유사합니다.

initial 또는 always를 순차적으로 사용하고 싶으면 begin and end를,

initial 또는 always를 병렬적으로 사용하고 싶으면 fork and join

ex)

initial fork

#2 a = 1;

#3 b = 1;

begin

#4 c = 1;

#2 d = 1; // c이후 10초 ∵ begin end 구문 안에서는 순차적으로 진행되므로

end

#5 e = 1;

join

| t | |

| 2 | a=1 |

| 3 | b=1 |

| 4 | c=1 |

| 5 | e=1 |

| 6 | d=1 |