안녕하세요,

UVM Testbench 작성 - WikiDocs 내용을 바탕으로 SystemVerilog에 대해 간단하게 정리해보았습니다.

Verilog는 많이 접해볼 수 있는데 SystemVerilog는 자료 찾기가 상대적으로 좀 힘들었던 것 같습니다.

이제 가볍게 훑어보면서 위키독스를 격파하도록 하겠습니다.

반도체 칩 구조가 점차 복잡해지면서 검증의 중요성과 비중 또한 높아지고 있습니다.

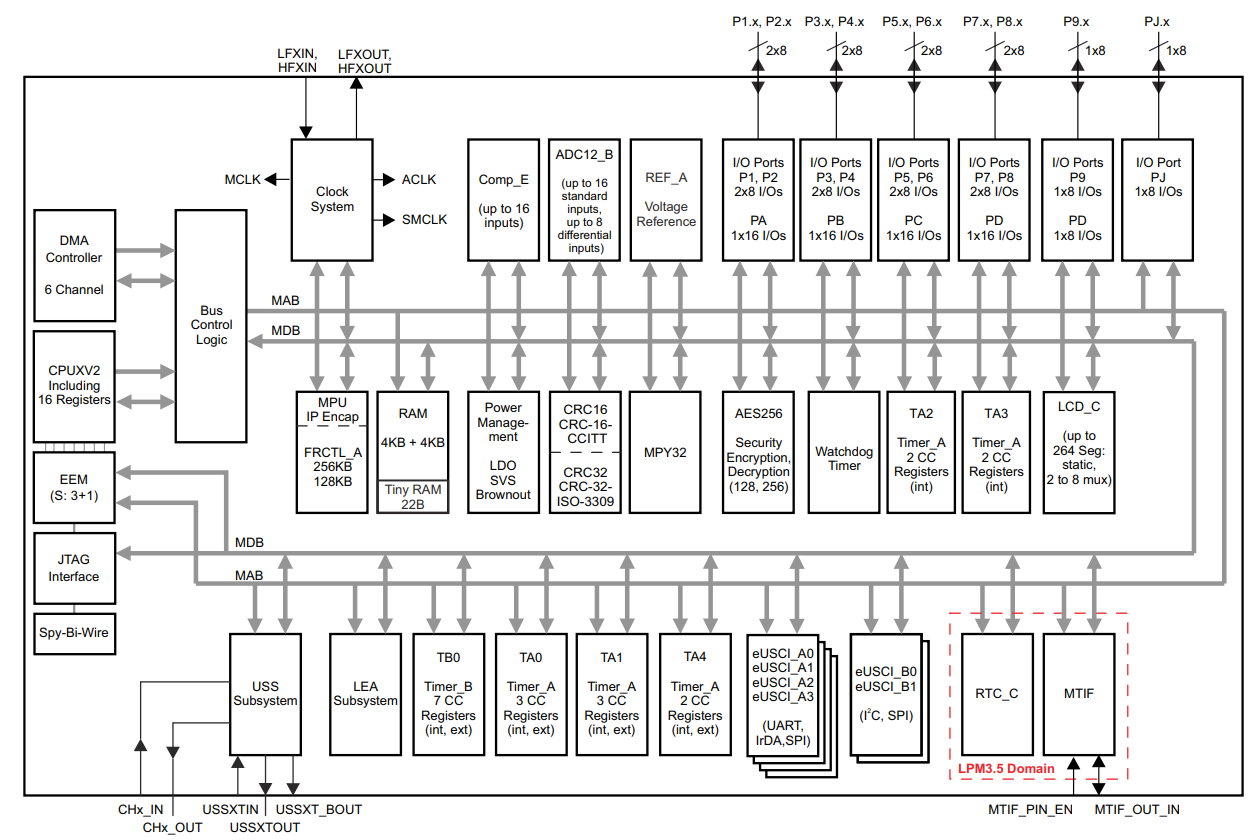

아래 그림은 SoC의 블록 다이어그램인데 이렇게 하나의 칩 내부는 여러 블록으로 구성되어 있습니다.

이 블록을 모듈 또는 IP(Intellectual Property, 이하 IP)라고 합니다.

과거에는 반도체 회사들이 IP를 직접 설계했지만, 이제는 IP 설계 업체로부터 검증된 IP를 구매해 칩을 설계합니다.

IP를 직접 설계하는 것보다 구는 것이 시간을 포함한 비용 측면에서 유리하기 때문입니다.

마치 식당에서 모든 재료를 직접 키우기보다는 좋은 거래처에서 사 오는 것과 비슷합니다.

기존에는 Verilog로 RTL 설계와 검증을 수행했습니다.

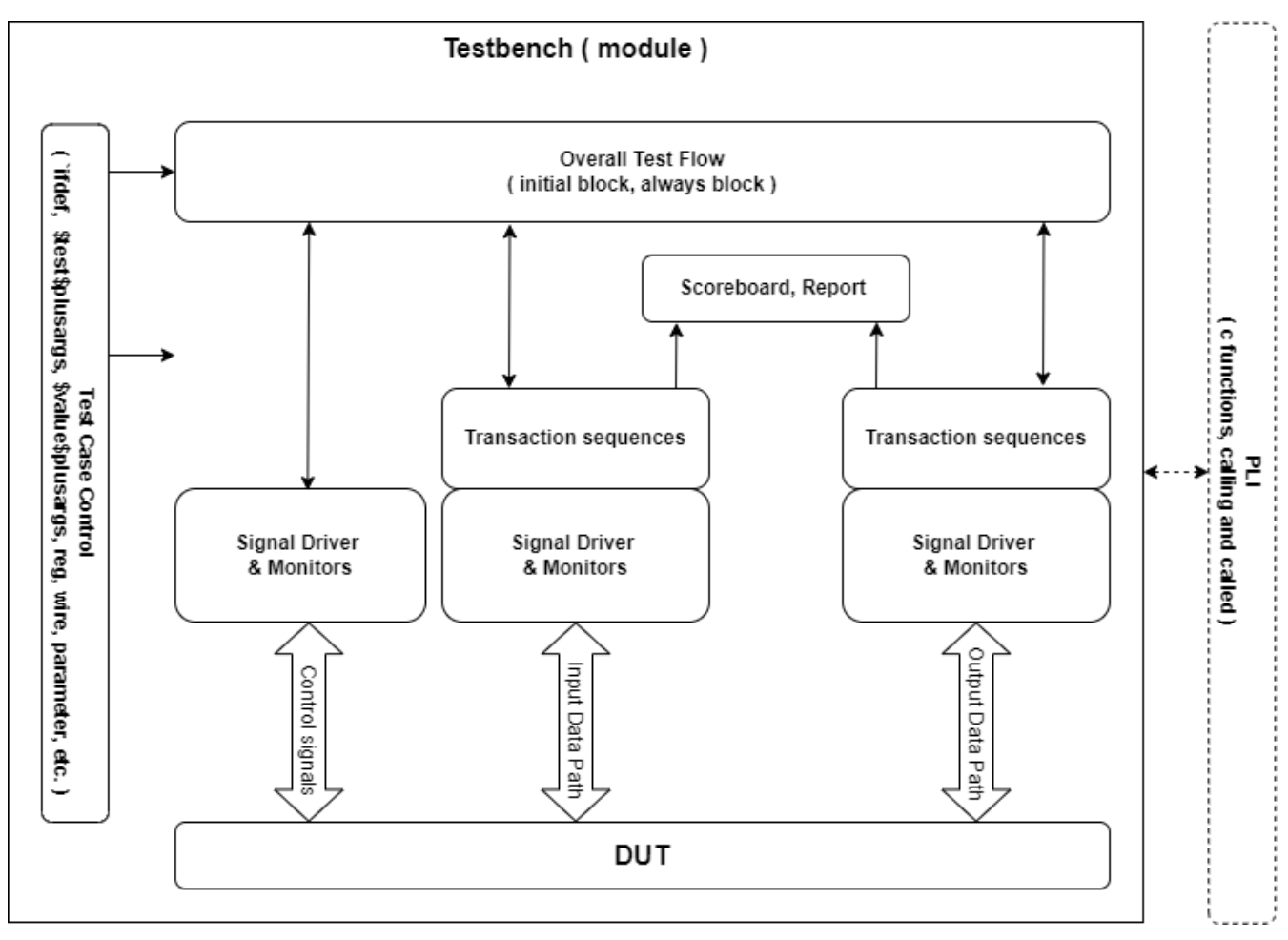

chip size가 점차 증가함에 따라 TB 역시 복잡해지고 규모가 커지게 되는데, 모듈 기반의 static 구조를 바탕으로 TestBench(이하 TB)를 설계하는 Verilog는 TB의 유연성과 확장성이 부족합니다.

아래의 Verilog TB에서 모든 모듈들을 기술해야 합니다.

또한 외부 Programming Language를 Interface 할 때와, Randomize 된 Test 수행 시 추가 작업들이 많이 필요합니다.

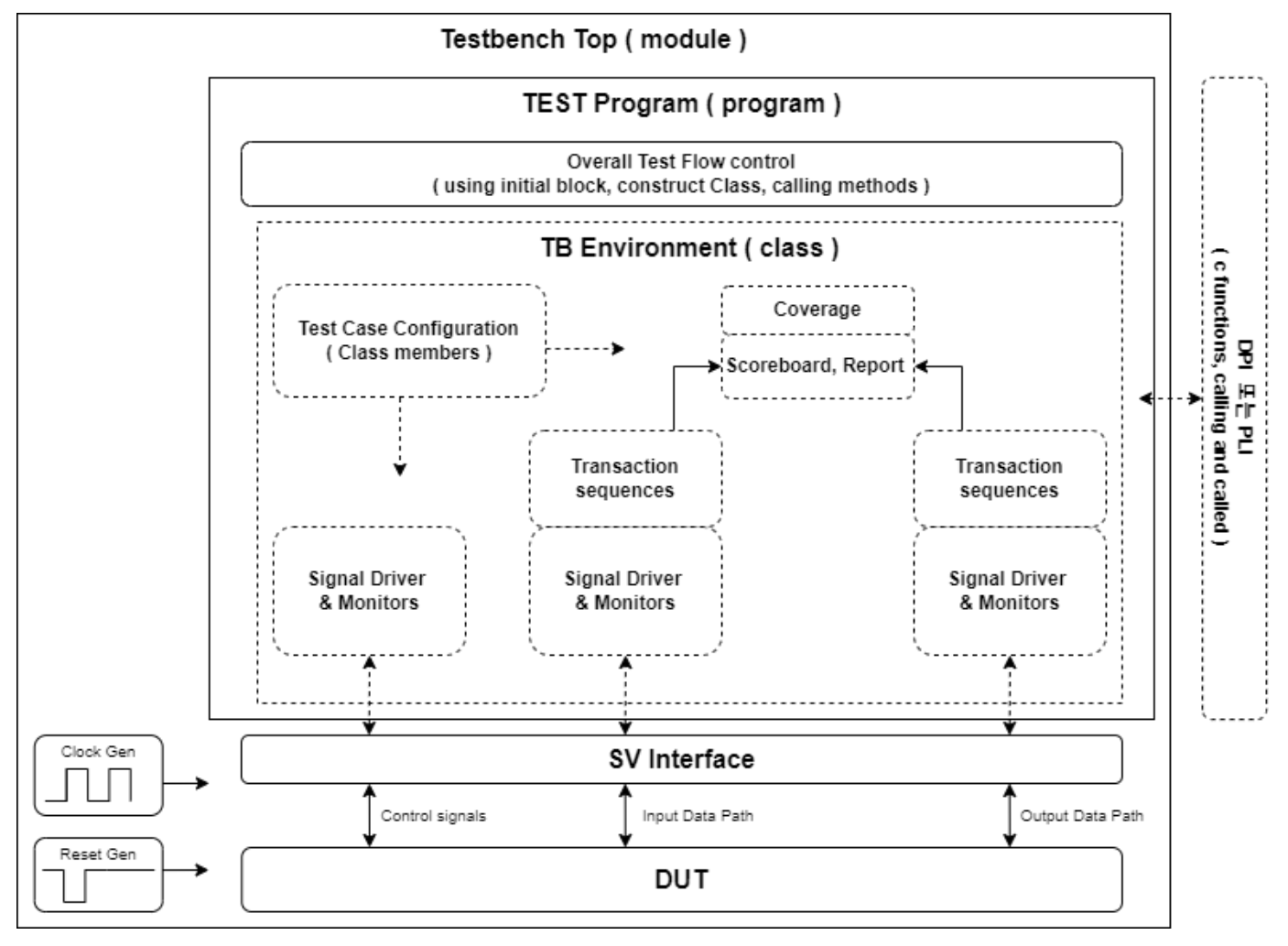

반면, SystemVerilog는 Static과 대비되는 Dynamic 개체인 class를 활용해 TB를 구현하므로, 더 효율적이며 고난도의 기능 구현이 가능합니다.

무엇보다 DUT와 Test Program을 SystemVerilog Interface로 연결함으로써 TB와 DUT의 독립적인 개발을 가능하게 합니다.

이 외에도 검증할 때 SystemVerilog의 장점을 상세하게 기술할 수 있으나 전체적으로 둘러보았습니다.

00.01 Simulation 환경 - UVM Testbench 작성

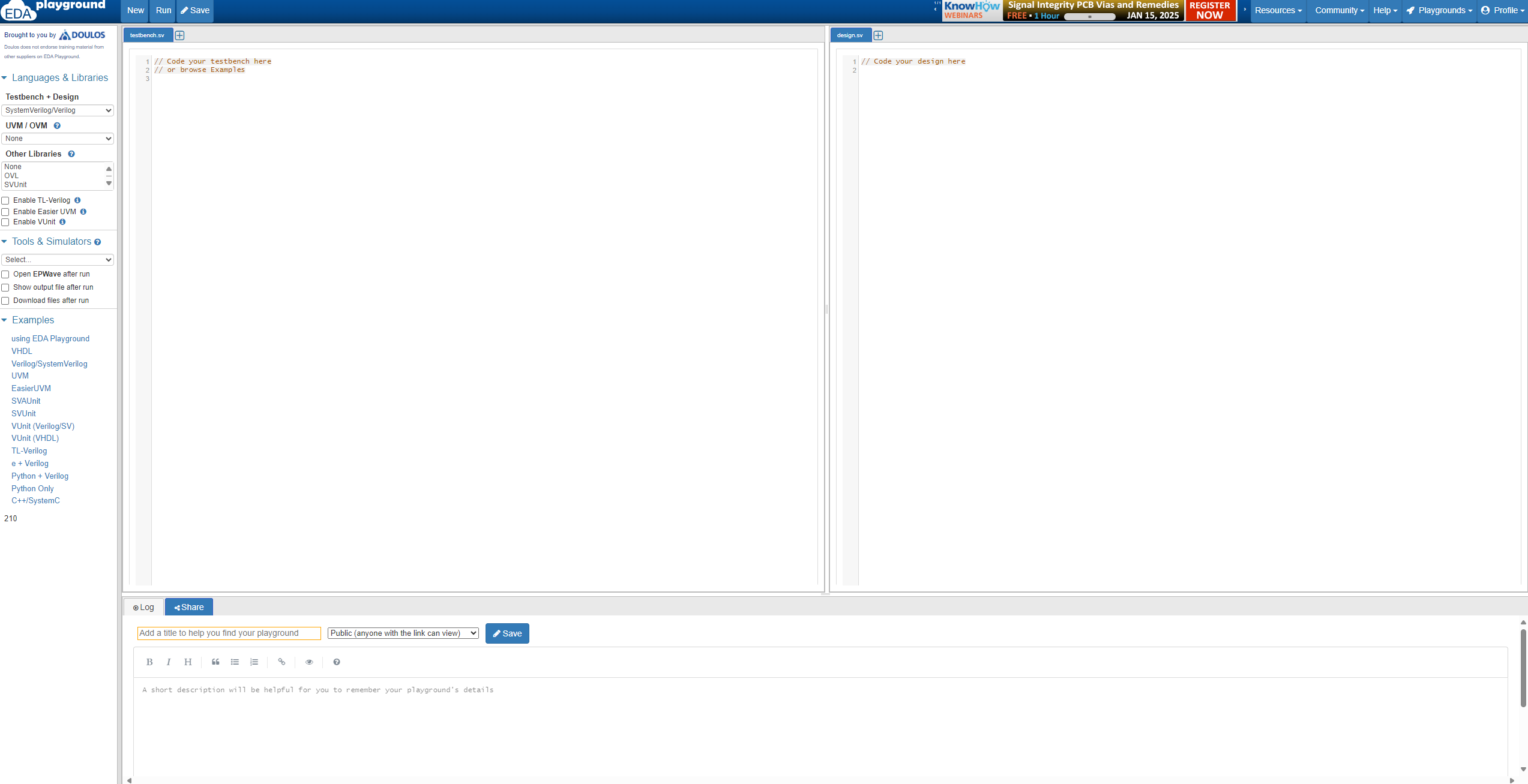

Simulation 환경은 EDA Playground를 사용합니다.

아래는 캡쳐한 Simulation 화면인데 왼쪽에는 TB를 오른쪽에는 DUT를 넣으면 됩니다.

01.04 SystemVerilog Testbench 작성 - UVM Testbench 작성 의 코드를 넣은 후

Testbench + Design은 SystemVerilog/Verilog 선택

Tools & Simulators는 Synopsys VCS 2023.03 선택

Save - Run을 수행하면 아래와 같이 Test 결과가 나옵니다.

이상으로 SystemVerilog에 대해 간단히 훑어보았습니다.