정의 : IEEE industry standard Hardware Description Language

IEEE(Institute of Electrical and Electronics Engineers)라는 "미국전자학회"가 규정한 디지털 시스템(하드웨어)을 표현하는 언어입니다.

구성 방법은 크게 3가지로 Behavior Modeling, Structural Modeling, RTL(Rester Transister Level) 방식이 있습니다.

Behavioral Modeling : 입력과 출력의 "관계"를 중심으로 표현합니다.

2 input multimplexer(모듈명 mux_2)를 구현했습니다. assign으로 입력과 출력의 관계를 정의했습니다.

module mux_2(

input [1:0] a, b,

input s,

output [1:0] y

);

assign y = s ? a : b;

endmodule

Structural Modeling : 기존 설계된 모듈을 바탕으로 상위 모델의 "구조" 중심으로 표현합니다.

4 input multiplexer(모듈명 mux_4)를 mux_2를 이용해 Structural Modeling 했습니다.

module mux_4(

input [1:0] a,b,c,d,

input [1:0] s,

output [3:0] y

);

wire [3:0] low, high;

mux_2 lowmux(a,b,s[0], low);

endmoduleRTL : behavior modeling의 중심으로 합성(Synthesis)을 위해 존재합니다.

Synthesis : Translating HDL to a circuit and then optimizing the represented circuit

즉, 합성이란 HDL(Hardware Description Language)를 회로로 변경하고 최적화하는 것입니다.

RTL Synthesis : Translating a RTL model of hardware into an optimized technology specific gate level implementation

그렇다면 RTL 합성을 RTL 모델의 하드웨어를 최적화된 특정 게이트 레벨 기술로 실행하는 것입니다.

RTL Synthesis와 Simulation Flow 전체적인 Flow입니다.

현재 저는 하만 세미콘 아카데미 교육 과정을 수강하고 있으며 Synthesis시 사용하는 tool은 Quatus를, Simulation은 Modelsim을 사용합니다.

특히 Place/Route 과정을 통해 SOF(Sram Object File)를 생성하고 이는 FPGA의 Pin mapping을 합니다.

이 과정이 없다면 FPGA 하드웨어에 구성한 코드를 실행할 수 없기에 꼭 필요합니다.

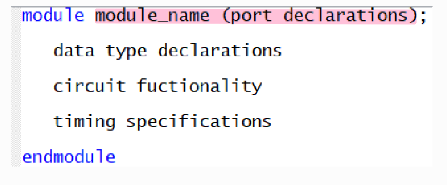

간단하게 문법을 알아보겠습니다.

- Verilog는 module로 시작하고 endmodule로 끝납니다.

- 대소문자를 구분합니다.

- 모든 keyword는 소문자입니다.

- 공백은 가독성을 위해 사용됩니다.

- C 언어와 같이 문장이 끝나면 ; 를 사용하고, 주석 처리 시, 1개의 문장은 //, 여러 문장은/* */을 이용합니다.

module_name (port declarations)

이름 앞에 숫자가 가장 먼저 올 수 없습니다. 모듈 이름과 Port list들을 선언해 줍니다.

port decalarations는 <port_type> port_name 형식입니다.

port_type은 input, output, inout 3가지가 있습니다.

ex) module my_adder(

input [1:0] dataa,

input [1:0] datab,

output [7:0] out

);

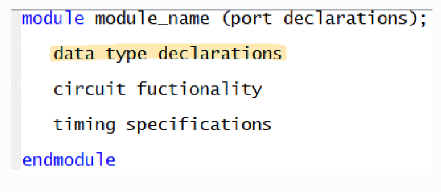

data type declarations

크게 net data type(대표 wire)과 variable data type(대표 reg)으로 구성되어 있습니다.

<data_type> [MSB : LSB] <signal name>; or <data_type> [MSB : LSB] <signal name>; 형식으로 표현합니다.

ex) wire [7:0] out; or reg [3:0] out;

circuit funtionality부터는 다음장에서 설명드리도록 하겠습니다.