하만 세미콘 아카데미 4기에서 진행한

Not, Nand, Nor Gate Stick Diagram과 Layout을 그려보도록 하겠습니다.

LVS와 DRC를 모두 확인했고, Stick Diagram의 대칭 형태로 그린 것이 많습니다.

아래의 게시물에서 각 Logic Gate에 맞는 Pmos의 Width 값을 찾았고 이를 바탕으로 Stick Diagram과 Layout을 그립니다.

https://semiconwide.tistory.com/53

Nand Gate 부터 Nand Flash까지, Cadence의 Virtuoso를 이용해 Nand Gate의 Pmos Width 찾기 시뮬레이션

안녕하세요, 이번 글에서는 2-Input Nand, Nor Gate에 대해 간단한 구조 설명 및 시뮬레이션 결과를 통한 Pmos의 Width를 찾아보겠습니다. 먼저 진리표입니다. Nand와 Nor가 And와 Or보다 구조가 단순하기에

semiconwide.tistory.com

Not Gate

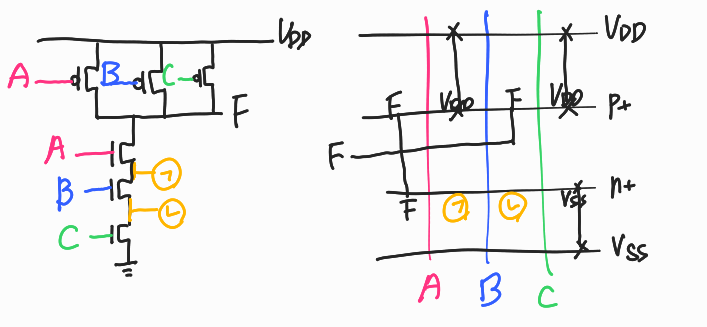

Nand Gate

(1) 2-Input Nand Gate

위 사진을 보시면 1번과 2번 형태로 나옵니다. 결론적으로는 1번의 형태가 좋은데 그 이유는 기생 캐패시터 때문입니다.

아래 그림을 보시면 diffusion 영역에서는 기생 캐패시터가 형성됩니다. 즉 diffusion이 많을수록 캐패시터의 병렬 연결로 값이 커집니다. 그렇게 되면 delay = RC에서 C값이 커지게 되므로 delay가 커지게 됩니다.

따라서 diffusion 영역을 최소화해야 합니다. 이후 다른 Gate 또한, diffusion 영역이 최소가 되도록 배선도를 만들었습니다.

(2) 3-Input Nand Gate

(3) 4-Input Nand Gate

Nor Gate

(1) 2-Input Nor Gate

(2) 3-Input Nor Gate

(3) 4-Input Nor Gate

드디어 Stick Diagr am대로 그려진 Gate입니다.

칩 면적이 최소화되도록 그리면서 얻은 점

1. 큰 면적을 차지하는 부품부터 배치를 맞춘다.

- 나중에 큰 면적을 차지하는 부분에서 수정이 필요하면 나머지 부분 전체를 수정해야 한다. 심할 경우 차라리 다시 그리는 것이 나을 정도로 그 과정이 너무나 험난하다.

2. 반드시, 한쪽 방향으로 그림을 그려나간다.

- 양쪽을 동시에 그리다가 수정할 방향이 나오지 않으면 둘 중 한쪽을 깡그리 수정해야 한다. 꼭 마진이 남도록 한 방향으로 그려나간다.

읽어주셔서 감사합니다.

'Layout' 카테고리의 다른 글

| Not, Nand, Nor Gate에 따른 Mosfet Width 비율 설정 (0) | 2023.07.08 |

|---|---|

| Nand Gate 부터 Nand Flash까지, Cadence의 Virtuoso를 이용해 Nand Gate의 Pmos Width 찾기 시뮬레이션 (2) | 2023.07.07 |

| Not Gate(Inverter) 완벽하게 정리하기(존재 이유부터 Width에 따른 VIN-VOUT 특성 분석) (0) | 2023.07.06 |