Not Gate(Inverte)는 입력이 0이면 출력이 1이고, 입력이 0이면 출력이 1인 논리 게이트입니다.

Pmos와 Nmos 1개로 구성된 Not Gate를 추가하면 2개의 mosfet을 추가한 것입니다. 이렇게 mosfet을 추가하면 power, speed, delay 등을 또 고려해야 하는데 왜! 단지, 0과 1을 반전하는 역할만 하는 Not Gate를 사용하는 것일까요?

바로 And와 Or Gate를 만들기 위해서는 Not Gate가 필수여서 개발됐습니다.

먼저 Nand와 Nor을 만든 후 그 값을 반전시켜야 And와 Or Gate를 만들 수 있습니다. 여기에 반전시키는 Not Gate가 필요한 것이죠. 이제 Nmos와 Pmos의 구조를 사진 2장으로 간단하게 파악 후 Not Gate에 대해 본격적으로 알아보겠습니다.

Nmos와 Pmos의 구조는 아래와 같습니다.

Nmos : Gate에 양전압이 걸려서 채널을 형성할 만큼의 전계가 생성됩니다. Source에서 Drain 방향으로 전자가 이동하니, 전류는 Drain에서 Source 방향으로 흐릅니다.

Pmos : Gate에 음전압이 걸려서 채널을 형성하는데 Body에 양전압을 가한 것으로 표현했습니다. Source에서 Drain 방향으로 양공이 이동하니, 전류는 Source에서 Drain 방향으로 흐릅니다.

이제 Not Gate을 보겠습니다.

입력 값 1(5V)이 들어올 때 : Pmos는 전계가 형성되지 않아 채널이 없고, Nmos는 전계와 채널이 형성됩니다.

그래서 Ground 값인 0을 출력합니다.

입력 값 0(0V)이 들어올 때 : Pmos는 전계와 채널이 형성되고, Nmos는 전계가 형성되지 않아 채널이 없습니다.

그래서 VDD 값인 1(5V) 출력합니다.

여기서 Not Gate에 대해 한 번 더 들어가기 위해 파악해야 것이 있으며 아래의 모스펫 전류 공식을 보도록 하겠습니다.

즉, 전류를 변화하기 위해서는 Cox나 Width(이하 L) 또는 Length(이하 L)를 변화해야 합니다.

하지만 Cox를 변경하려면 이미 사용되는 Cox 값이 맞춰진 공정이 끝난 이후에 다시 작업이 들어가야 합니다.

그래서 보통 W와 L을 변화시키죠.

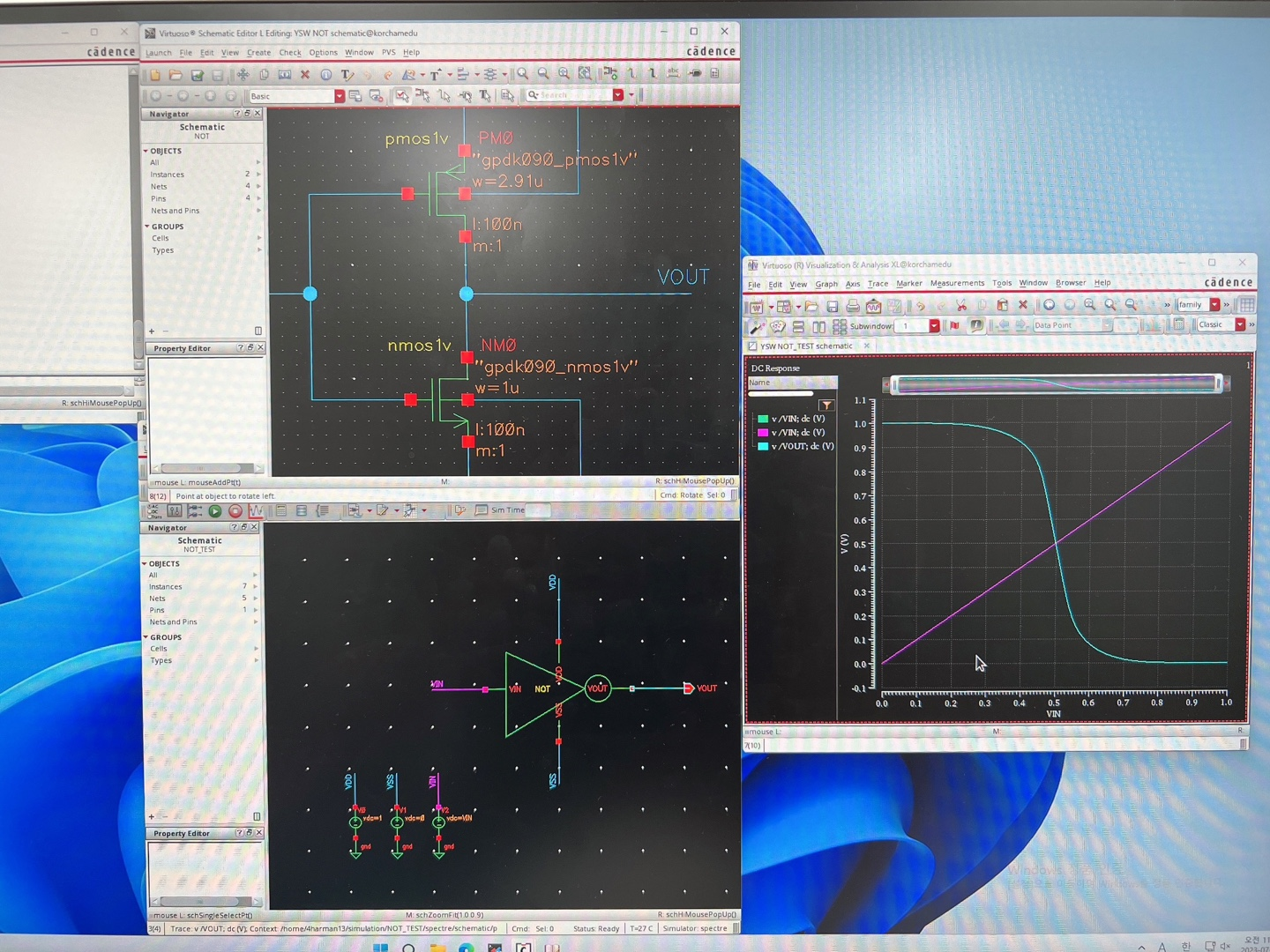

하만 세미콘 아카데미에서 W 값에 따른 Not Gate의 특성을 Cadence의 Virtuoso 프로그램을 이용해 분석했습니다.

이상적인 Not Gate는 오른쪽 그림같이 대칭이고, 그 이유는 Swing을 고려해야 하기 때문이라고 간단하게 알아두겠습니다.

특히 VIN과 VOUT 0V~1V까지인 위의 경우 대칭이며 교점이 0.5V, 0.5V인 그래프가 이상적입니다.

Pmos의 W=2um를, Nmos의 W=1um를 넣었으나 그래프의 형태가 이상적이지 않았습니다.

이제 이상적인 Not Gate를 만드는 Pmos의 W를 찾아보도록 하겠습니다.

아래는 W=1um부터 10um까지 1u씩 변화시키며 나온 VIN-VOUT 그래프입니다.

0.5V, 0.5V를 지나도록 하는 Pmos의 W는 2um와 3um 사이에 있으며 3um에 좀 더 가깝다는 것을 알 수 있습니다.

그래서 아래와 2um부터 3um까지 0.1um 간격으로 변화시켰고 그 결과 VIN-VOUT 그래프입니다.

0.5V, 0.5V를 지나도록 하는 Pmos의 W는 2.9um와 3um 사이에 있으며 2.9um에 좀 더 가깝다는 것을 알 수 있습니다.

그래서 마지막으로 2.9um부터 3um까지 0.01um 간격으로 변화시켰고 2.91um가 가장 이상적임을 확인했습니다.

마지막인 이유는 virtuso 프로그램 상 소수점 2번째 자리까지 계산할 수 있기 때문입니다.

시뮬레이션으로 구한 Pmos의 Width(2.91um)는 Nmos의 Width(1um)의 2.91배입니다.

위의 전류 식에서 같은 항을 지워보니 위 소자는 결국 전자의 모빌리티가 2.91배라는 것을 파악할 수 있습니다.

읽어주셔서 감사합니다.

'Layout' 카테고리의 다른 글

| Not, Nand, Nor Gate Stick Diagram, Layout 그리기 (6) | 2023.07.25 |

|---|---|

| Not, Nand, Nor Gate에 따른 Mosfet Width 비율 설정 (0) | 2023.07.08 |

| Nand Gate 부터 Nand Flash까지, Cadence의 Virtuoso를 이용해 Nand Gate의 Pmos Width 찾기 시뮬레이션 (2) | 2023.07.07 |