안녕하세요, 이 글을 보러 오시는 분들은 대부분 Edge Trigger와 Level Triger의 차이를 알고 싶으실 것입니다.

먼저 Edge Trigger와 Level Trigger 차이를 보고, Edge Trigger의 동작 원리를 보겠습니다.

Edge Trigger는 Clock Pulse가 Rising or Falling Edge에서'만' Data를 캡처하고,

Level Trigger는 Clock Pulse가 High or Low에서만 Data를 캡처합니다.

Clock Pulse가 Rising or Falling Edge인 시간이 High or Low 되는 시간보다 짧기에 Datat를 잘 캡처할 수 있습니다.

즉, High or Low인 시간은 상대적으로 길기에 중간에 상태가 변화할 수도 있어 Data 캡처에 실패할 가능성이 높습니다.

그렇기에 시스템 안정성을 위해 Edge Trigger를 주로 사용합니다.

단 이로 인한 Trade off 효과는 Flip-Flop을 사용하기에 소자가 더 많이 사용된다는 것입니다

간략하게 Edge Trigger와 Level Triger의 개념을 잡았고, 이제 Edge Trigger 동작 원리를 알아보겠습니다.

어떤 동작을 하길래 Rising or Falling Edge에서'만' 데이터를 캡처할 수 있을까?라고 하기 전에 드릴 말씀이 있습니다.

몇 년간 짬짬이 시간을 내서 자료를 찾아봤지만 Edge Trigger 동작을 제대로 설명하는 블로그를 찾을 수 없었습니다.

설명 방식이 각자 다를 뿐만 아니라 "그래서 결국 Edge Trigger가 어떻게 동작하는데?"라는 질문에 대한 답변을 들을 수 없었습니다. 진짜 디지털 쓰레... 여기까지 하겠습니다.

하지만 https://m.blog.naver.com/tb_elec_engineer/221034769694 이곳의 제대로 된 설명 통해 드디어 이해할 수 있었습니다. 여기에 제 설명을 보태서 한 번에 제대로 설명한 Edge Trigger(에지 트리거)의 동작 원리를 말씀드리겠습니다.

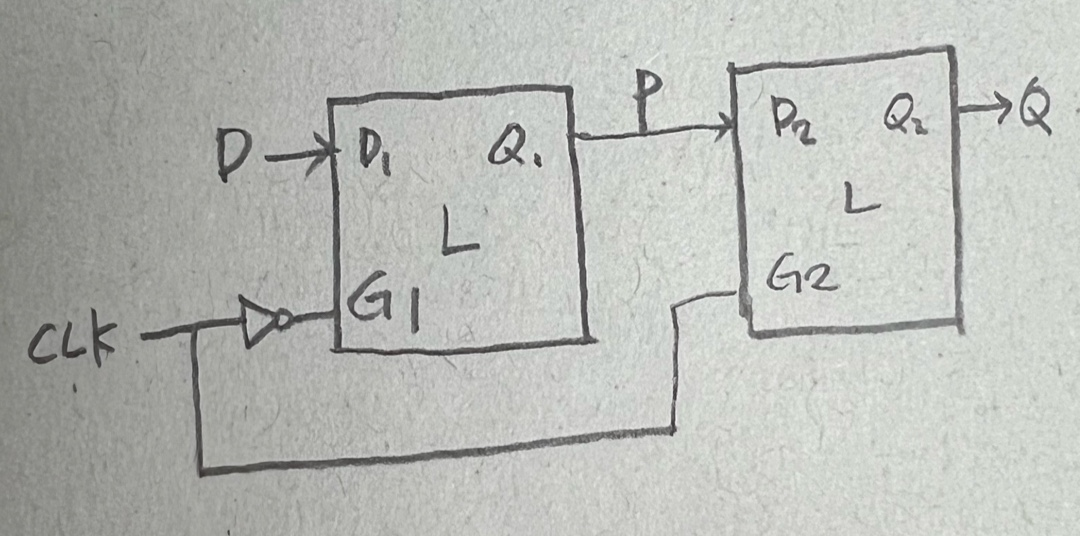

R-S Latch → D Latch → D Flip-Flop순으로 진행하겠습니다. D latch 2개가 붙으면 D Filp-Flop이 됩니다.

R-S Latch를 표현하는 다양한 Gate 방식이 있지만 Nor Gate를 사용하면 아래와 같습니다.

다음은 진리표입니다. Q+는 Q'가 아니며 Q는 현재 상태이고 Q+는 다음 상태입니다.

| R | S | Q | Q+ |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | x |

| 1 | 1 | 1 | x |

위의 빨간 음영 부분에서 S = 1 이면 Q+는 Q의 값과 관계없이 1이며, 위의 파란 음영 부분에서 R = 1 이면 Q+는 Q의 값과 관계없이 0입니다. 그리고 R = S = 0 이면 Q = Q+로 이전 값을 그대로 따라갑니다.

R = S = 1인 상황이 발생하면 Q+ 값에 문제가 생깁니다. 이를 방지하기 위해 Gate형 D Latch 회로가 있습니다.

이렇게 되면 D가 1, 0 어떤 값이 되더라도 And Gate에 의해 S와 R에 둘 다 1이 될 수 없습니다.

이제 Gate형 D Latch의 특성을 분석해 보겠습니다. G와 D는 제가 임의로 설정한 파형입니다.

1칸당 1ns로 보겠습니다. 그럼 G가 0 → 1 인 시점은 3ns가 되는 것이죠.

3ns까지 G = 0이면 S, R 모두 0입니다. 그래서 Q도 0입니다.

3ns부터 G가 0 → 1 이면서 (D = 1일 때 S = 1, R = 0), (D = 0일 때 S = 0, R = 1) 이 됩니다.

그리고 위의 진리표에 의해 Q 값이 결정됩니다.

별표 친 8ns인 G가 1 → 0 인 순간 S와 R 모두 0이 됩니다. 그리고 진리표에 의해 Q 값은 이전 값을 유지합니다.

Gate형 D Latch의 진리표는 다음과 같습니다.

| D | Q | Q+ |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

D = Q+입니다.

이것이 Level Trigger인 Latch입니다. G = 1일 때 Q가 바뀌게 됩니다.

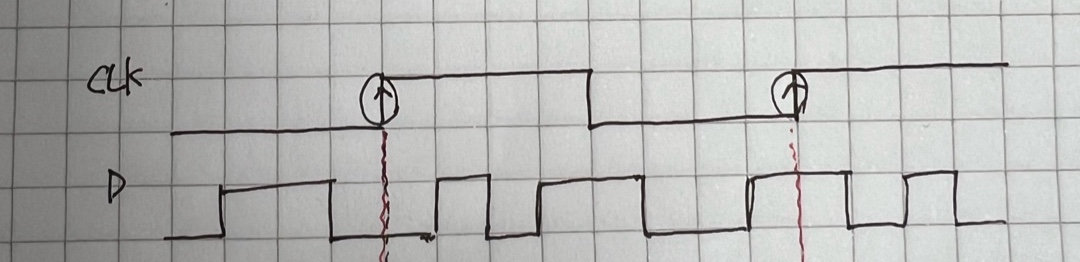

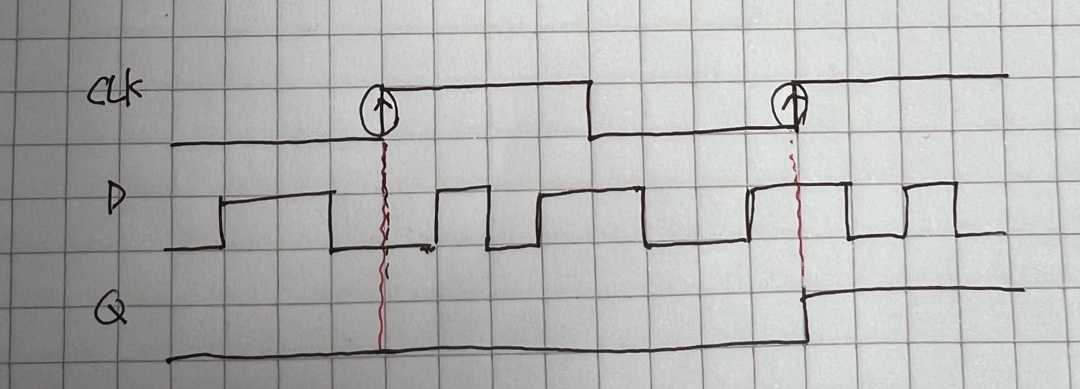

자 이제 마지막 D Flip-Flop을 보겠습니다. 아래 CLK과 D의 파형이 나와있습니다.

Rising Edge에서 D를 캡처한 Q 값은 다음과 같습니다.

RIsing Edge인 순간 D의 값을 저장하고 다음 Rising Edge까지 유지합니다.

이렇게 하기 위해서는 다음과 같은 Flip-Flop이 필요합니다.

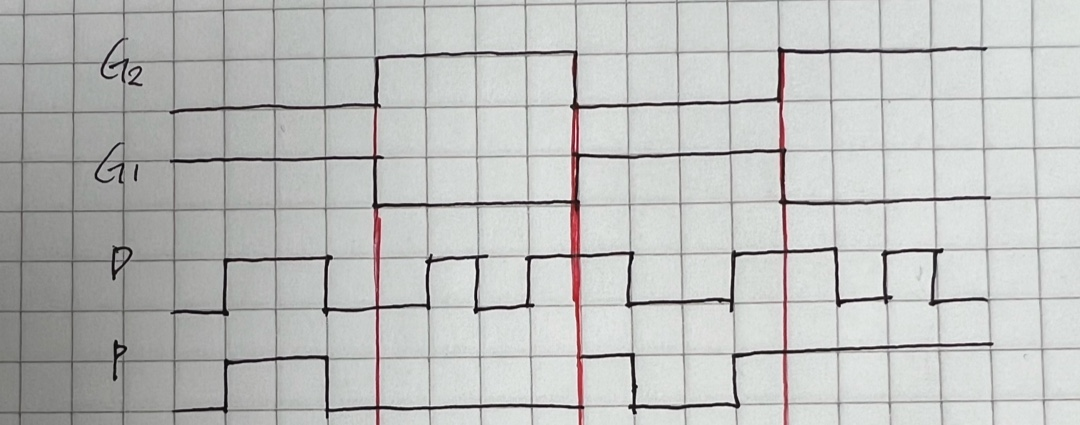

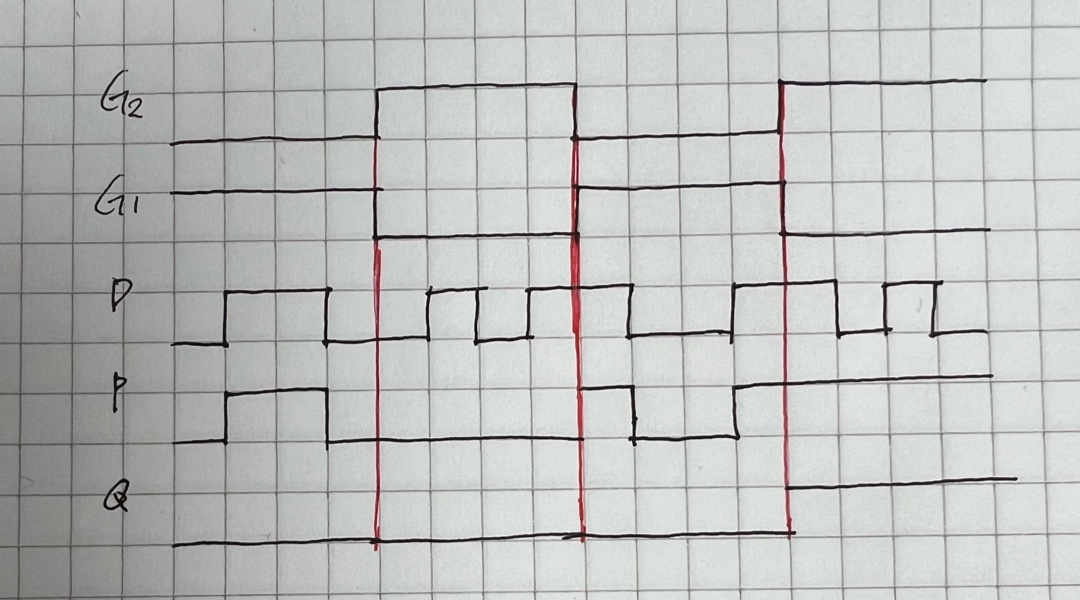

아래와 같이 G1과 D의 파형을 설정한 후 P의 파형을 먼저 보겠습니다. G1이 설정되면 G2는 인버팅 된 신호가 들어갑니다.

P는 G1 = 1일 때 값이 변화며 이는 Gate형 D Latch에 따라 변화합니다.

이제 이 P형에 G1까지 고려하면 결국 Q는 다음과 같은 파형이 됩니다.

결국 Q 값은 Rising Edge에서 D 값을 캡처한 값이 설정되므로 Edge Trigger로 동작합니다.

읽어주셔서 감사합니다. 질문과 피드백은 언제든지 환영합니다.

'Electrical Study' 카테고리의 다른 글

| STM32CubeIDE에 NUCLEO-F103RB GPIO 출력 파형 찍어보기 (0) | 2025.02.18 |

|---|---|

| STM Project 사용된 하드웨어 및 개발 환경 (0) | 2025.02.18 |

| 제일 쉽게 I2C를 알아보자 (3) | 2023.11.20 |

| 수동 소자 R, L, C에서 C와 L의 전압, 전류 특성 알아보기 (0) | 2023.10.03 |

| EMI/EMS/EMC에 대한 뜻과, EMI 발생 원인 (0) | 2023.09.28 |